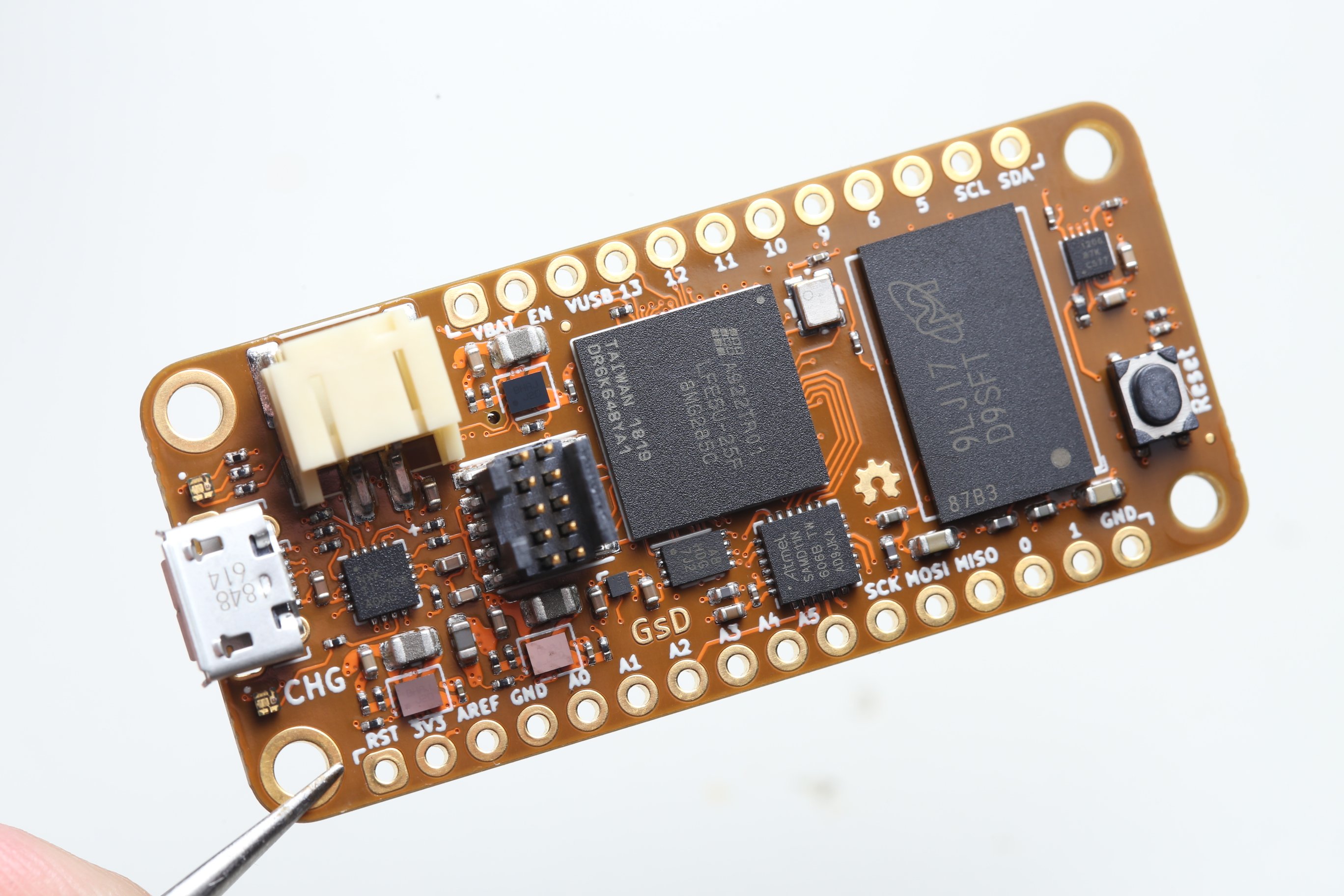

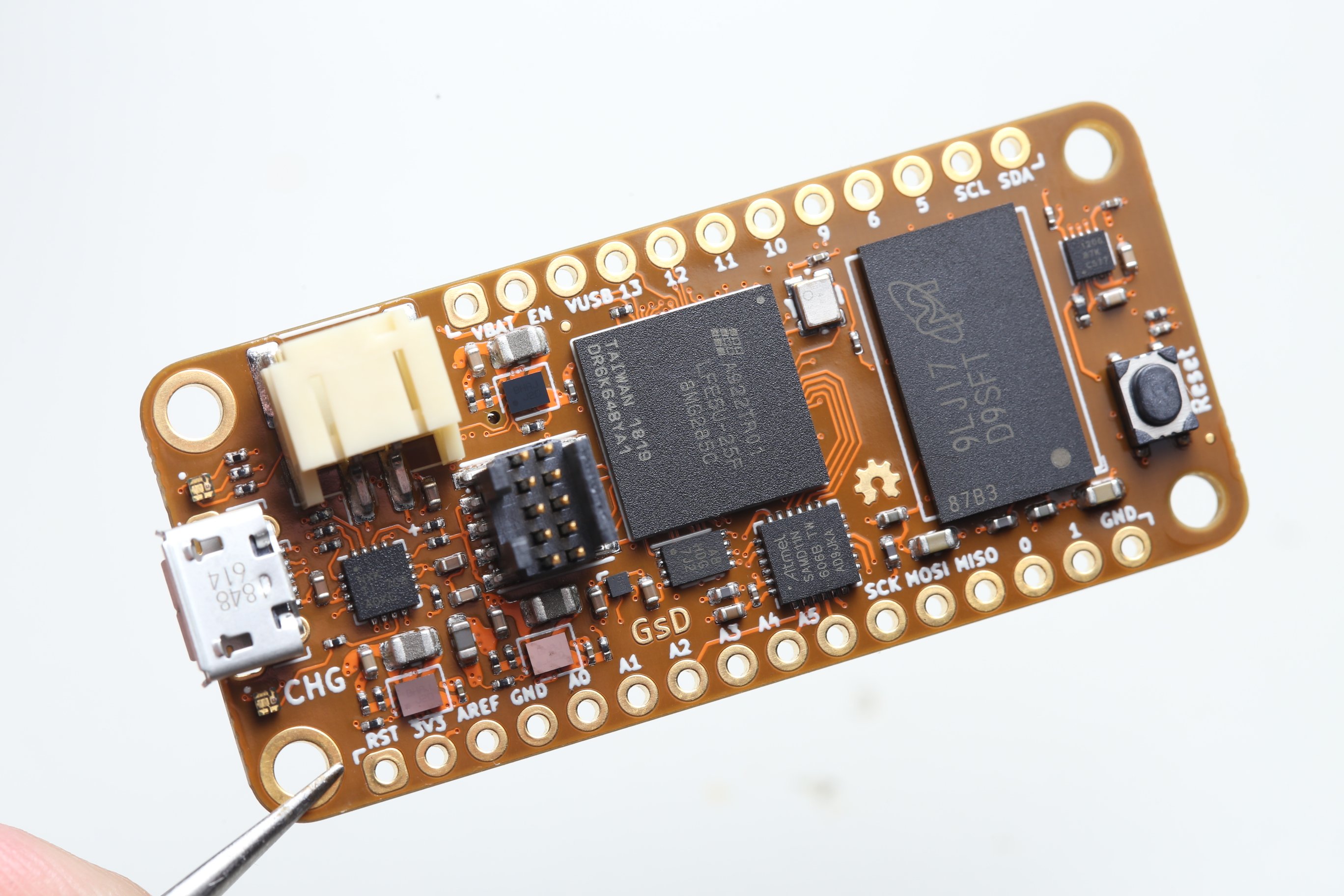

Description #

Initial version of the OrangeCrab, an electronics development board featuring a Lattice ECP5 FPGA, and DDR3 memory. Primarily designed to prototype RISCV SoC and evaluate custom peripherals.

Technical details #

- Lattice ECP5 25 (With limited support for 45/85 variants)

- DDR3L Memory upto 1Gbit (64Mbit x16)

- Micro USB connection

- Full-speed (12Mbit) USB direct connection to FPGA

- Battery charger, with charge indicator LED

- Reset Button

- 16Mbit QSPI FLASH Memory (Bitstream + User storage)

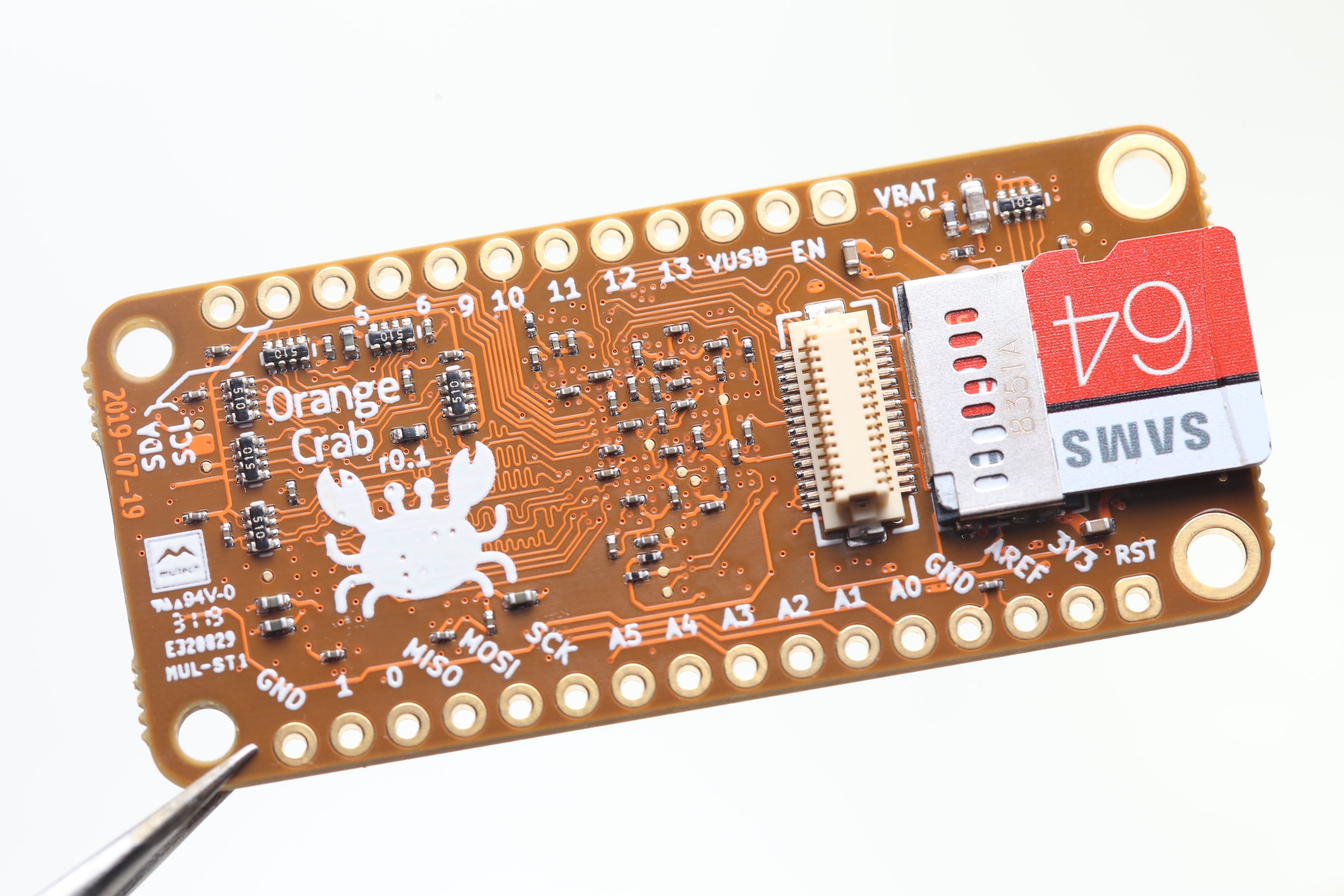

- 4bit MicroSD socket

- 48MHz Oscillator (Used by USB system)

- ATSAMD10/11 Co-processor planned mainly for the ADC/DAC

- Spare 3.3V I/O’s broken out onto a 30pin low profile connector

- 7 diff pairs

- 1 single ended only

Photos #